关于晶振电路真的简单吗?如何可靠的设计好GD32晶振电路,我们需要知道这些:

1、GD32可以选择哪些范围大小晶振?

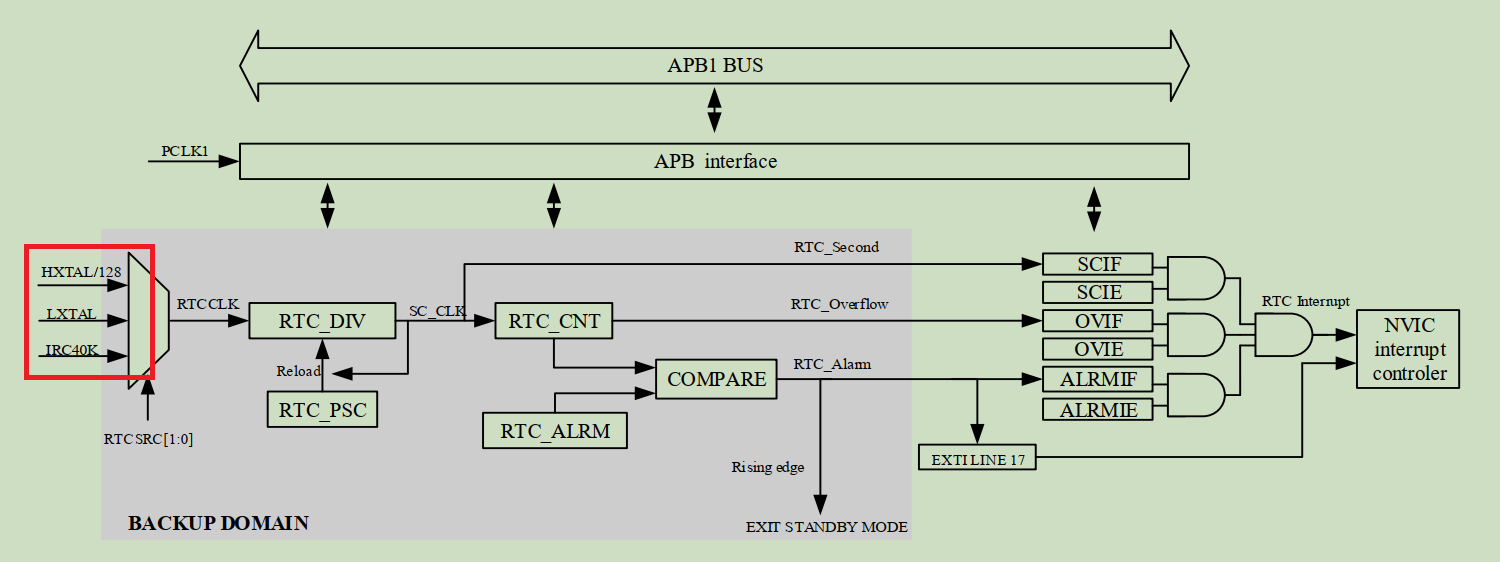

以GD32F303为例,查询DATASHEET外部时钟电气特性小节可以看到晶振支持范围是4—32M范围均可选择

2、需不需要反馈电阻?

反馈电阻可以使芯片内部反相器稳定工作在线性区间,虽然一般MCU内部是设计有反馈电阻的,但根据晶振频率不同,反馈电阻的范围会有区别,所以可以根据晶振频率来选择合适阻值的反馈电阻,典型的反馈电阻取值范围如下表,根据GD32F303的晶振范围,1MΩ基本可以全区间要求。

3、外部匹配电容该用多大?

负载电容对晶振稳定性至关重要,晶振的规格书中一般会给出推荐的负载电容值,但实际负载电容需要外部匹配电容和PCB走线杂散电容来综合计算。一般我们采用如下公式计算:

其中Cs是PCB杂散电容,可取典型值10pF,再根据晶振规格书的CL值要求,我们就可以计算出CL1和CL2所需大小。

4、需不需要阻尼电阻?

阻尼电阻跨接在OSC_OUT晶振引脚之间,一方面可以限流避免晶振过振荡,另一方面和匹配电容可以组成RC滤波,设置合适阻值大小将RC电路截止频率设置为振荡频率可以滤除噪声,经过公式推算阻值大小可以按如下公式计算:

合适的阻尼电阻还可以降低EMI噪声,提高MCU内部模拟性能等,非常建议大家设计预留。

5、PCB Layout

PCB 走线应尽量和高频 数字信号或其他噪声源隔离,可以使用接地环或接地平面进行包裹。

晶振应靠近MCU,减少走线长度避免其他信号干扰。

IN和OUT信号应该尽量保持相近走线长度,避免走线寄生电容差异导致匹配电容不一致。

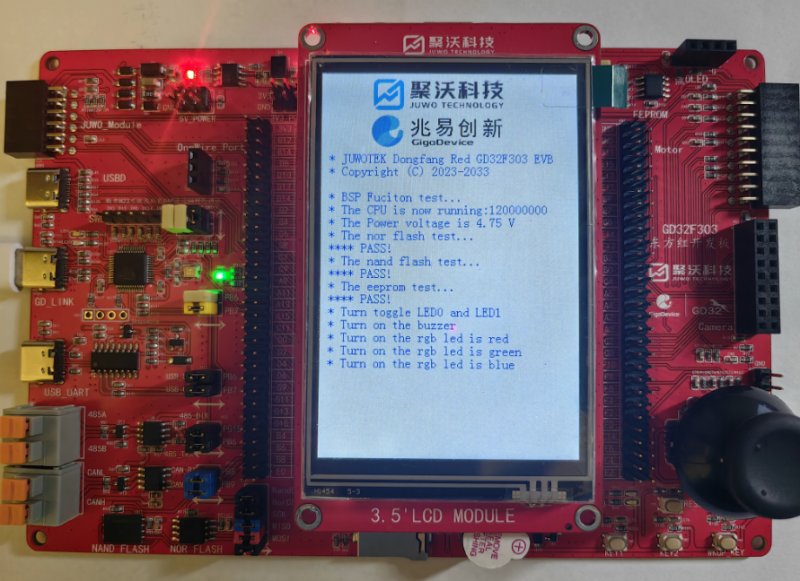

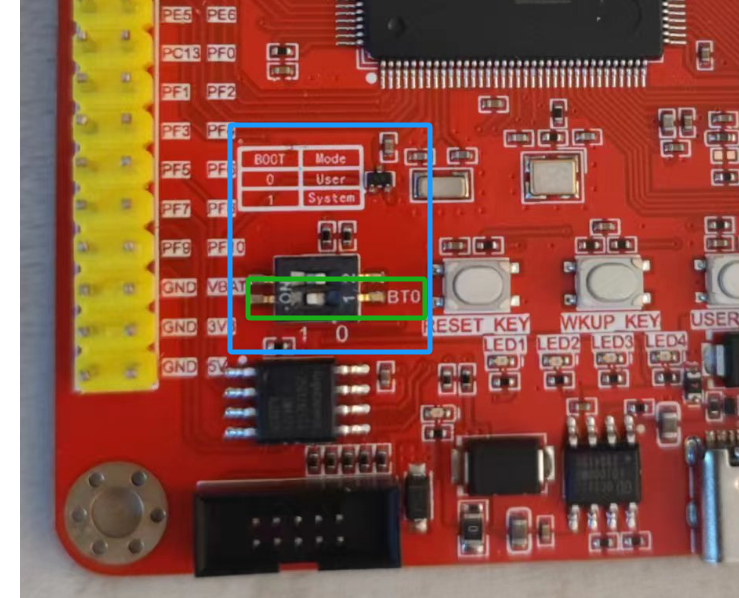

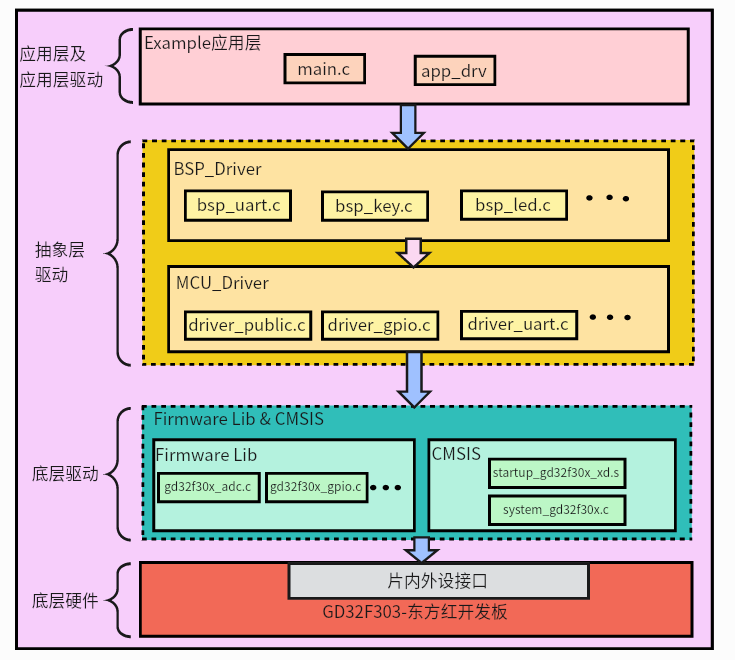

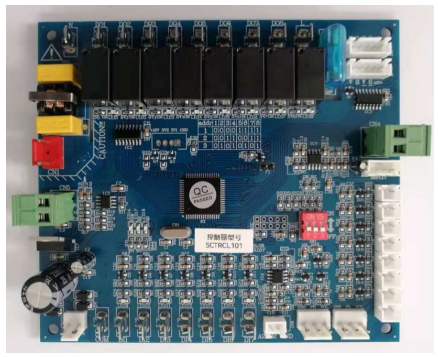

关于更多电路设计,可以参考聚沃科技GD32F303东方红开发板。

发表评论 取消回复